# PIC16F193X/LF193X データシート

28/40/44 ピン フラッシュ ベース、8 ビット CMOS マイクロコントローラ (LCD ドライバおよびナノワット XLP™ テクノロジ対応)

> ご注意: この日本語版ドキュメントは、参考資料としてご使用の上、最新情報に つきましては、必ず英語版オリジナルをご参照いただきますようお願い します。

#### マイクロチップ テクノロジー社(以下、マイクロチップ社)デバイスのコード保護機能に関する以下の点にご留意ください。

- マイクロチップ社製品は、その該当するマイクロチップ社データシートに記載の仕様を満たしています。

- マイクロチップ社では、通常の条件ならびに仕様どおりの方法で使用した場合、マイクロチップ社製品は現在市場に流通している同種製品としては最もセキュリティの高い部類に入る製品であると考えております。

- コード保護機能を解除するための不正かつ違法な方法が存在します。マイクロチップ社の確認している範囲では、このような方法のいずれにおいても、マイクロチップ社製品をマイクロチップ社データシートの動作仕様外の方法で使用する必要があります。このような行為は、知的所有権の侵害に該当する可能性が非常に高いと言えます。

- マイクロチップ社は、コードの保全について懸念を抱いているお客様と連携し、対応策に取り組んでいきます。

- マイクロチップ社を含むすべての半導体メーカーの中で、自社のコードのセキュリティを完全に保証できる企業はありません。コード保護機能とは、マイクロチップ社が製品を「解読不能」として保証しているものではありません。

コード保護機能は常に進歩しています。マイクロチップ社では、製品のコード保護機能の改善に継続的に取り組んでいます。マイクロチップ社のコード保護機能を解除しようとする行為は、デジタルミレニアム著作権法に抵触する可能性があります。 そのような行為によってソフトウェアまたはその他の著作物に不正なアクセスを受けた場合は、デジタルミレニアム著作権法の定めるところにより損害賠償訴訟を起こす権利があります。

本書に記載されているデバイス アプリケーションなどに 関する情報は、ユーザーの便宜のためにのみ提供されて いるものであり、更新によって無効とされることがあり ます。アプリケーションと仕様の整合性を保証すること は、お客様の責任において行ってください。マイクロチッ プ社は、明示的、暗黙的、書面、口頭、法定のいずれであ るかを問わず、本書に記載されている情報に関して、状 態、品質、性能、商品性、特定目的への適合性をはじめと する、いかなる類の表明も保証も行いません。マイクロ チップ社は、本書の情報およびその使用に起因する一切の 責任を否認します。マイクロチップ社デバイスを生命維持 および/または保安のアプリケーションに使用することは デバイス購入者の全責任において行うものとし、デバイス 購入者は、デバイスの使用に起因するすべての損害、請 求、訴訟、および出費に関してマイクロチップ社を弁護、 免責し、同社に不利益が及ばないようにすることに同意す るものとします。暗黙的あるいは明示的を問わず、マイク ロチップ社が知的財産権を保有しているライセンスは一 切譲渡されません。

#### 商標

Microchip の社名とロゴ、Microchip ロゴ、dsPIC、 KEELOQ、KEELOQ ロゴ、MPLAB、PIC、PICmicro、 PICSTART、rfPIC、UNI/O は、米国およびその他の国に おける Microchip Technology Incorporated の登録商標です。

FilterLab、Hampshire、HI-TECH C、Linear Active Thermistor、MXDEV、MXLAB、SEEVAL、The Embedded Control Solutions Company は、米国における Microchip Technology Incorporated の登録商標です。

Analog-for-the-Digital Age、Application Maestro、CodeGuard、dsPICDEM、dsPICDEM.net、dsPICworks、dsSPEAK、ECAN、ECONOMONITOR、FanSense、HI-TIDE、In-Circuit Serial Programming、ICSP、ICEPIC、Mindi、MiWi、MPASM、MPLAB Certified ロゴ、MPLIB、MPLINK、mTouch、nanoWatt XLP、Omniscient Code Generation、PICC、PICC-18、PICkit、PICDEM、PICDEM.net、PICtail、PIC<sup>32</sup> ロゴ、Real ICE、rfLAB、Select Mode、Total Endurance、TSHARC、WiperLock、ZENA は、米国およびその他の国における Microchip Technology Incorporated の商標です。

SQTP は米国における Microchip Technology Incorporated のサービスマークです。

その他、本書に記載されている商標は、各社に帰属します。 © 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

乗生紙を使用しています。

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002 ===

マイクロチップ社では、Chandler およびTempe (アリゾナ州)、Gresham (オレゴン州)の本部、設計部およびウエハ製造工場そしてカリフォルニア州とインドのデザイン センターが ISO/TS-16949:2002 認証を取得しています。マイクロチップ社の品質システム プロセスおよび手順は、PIC® MCU および dsPIC® DSC、KEELOQ® コード ホッピング デバイス、シリアル EEPROM、マイクロペリフェラル、不揮発性メモリ、アナログ製品に採用されています。また、マイクロチップ社の開発システムの設計および製造に関する品質システムは、ISO 9001:2000 の認証を受けています。

### 28 ピン /40 ピン /44 ピン、フラッシュベースの LCD ドライバ付き 8 ビット CMOS マイクロコントローラ (nano Watt XLP™ テクノロジに対応)

#### このデータシートに記載されているデバイス

#### PIC16F193X デバイス:

- PIC16F1933

- PIC16F1936

- PIC16F1937 • PIC16F1939

- PIC16F1938

#### PIC16LF193X デバイス:

- PIC16LF1933

- PIC16LF1934

PIC16F1934

- PIC16LF1936

- PIC16LF1937

- PIC16LF1938

- PIC16LF1939

#### 高性能 RISC CPU:

- わずか49個の命令:

- 命令はすべて1サイクルで実行(条件分岐を除く)

- 動作速度:

- DC 32 MHz のオシレータ / クロック入力

- DC 125 ns の命令サイクル

- 最大 16K x 14 のフラッシュ プログラム メモリ

- 最大 1024 バイトのデータ メモリ (RAM)

- 割り込み機能(自動で内容保存)

- 16 段のハードウェア スタック

- 直接、間接、相対のアドレッシングモード

- プロセッサによるプログラム メモリの読み出し

- 28/40 ピン PIC16CXXX および PIC16FXXX マイ クロコントローラとピン互換

#### このマイクロコントローラの機能:

- 高精度内部オシレータ:

- 工場にて±1%(標準)に較正

- 動作周波数はソフトウェアで 32 MHz ~ 31 kHz の範囲内で選択可能

- 省電力スリープモード

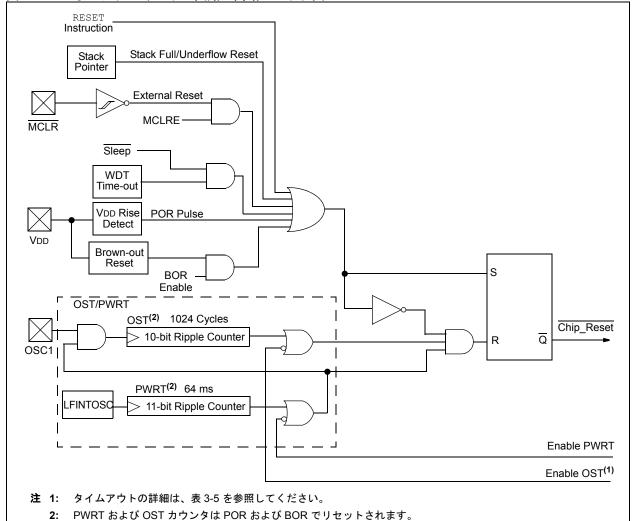

- パワーオン リセット (POR)

- パワーオン タイマ (PWRT) およびオシレータ スタートアップ タイマ (OST)

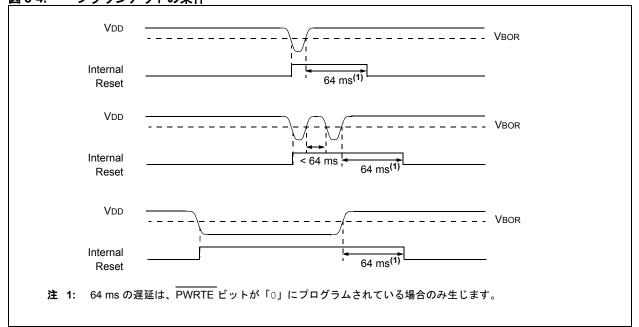

- ブラウンアウト リセット(BOR)

- 2つのトリップポイントから選択可能

- スリープ オプションで無効

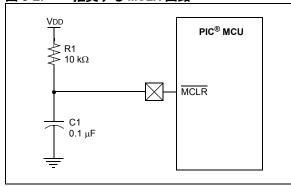

- プルアップ / 入力ピンで多重化されたマスター クリア

- プログラム可能なコード プロテクション

- 耐久性の高いフラッシュ /EEPROM セル:

- 10 万回の書き換えを保証するフラッシュ

- 100 万回の書き換えを保証する EEPROM

- フラッシュ/データ EEPROM 保持時間:>40 年超

- 広い動作電圧範囲:

- $1.8V \sim 5.5V (PIC16F193X)$

- $1.8V \sim 3.6V (PIC16LF193X)$

#### 低消費電力 PIC16LF193X:

- スタンバイ電流:

- 60 nA @ 1.8V (標準)

- 動作時電流:

- 7.0 μA @ 32 kHz、1.8V (標準)

- 150 μA @ 1 MHz、1.8V (標準)

- Timerl オシレータ電流:

- 600 nA @ 32 kHz、1.8V (標準)

- 低電力ウォッチドッグ タイマ電流:

- 500 nA @ 1.8V (標準)

#### 周辺機能の特徴:

- 最大 35 個の I/O ピンおよび 1 個の入力専用ピン:

- LED 直接駆動用の高電流ソース / シンク

- 個別に設定可能な状態変化割り込みピン

- 個別に設定可能な弱プルアップ

- ・ 統合された LCD コントローラ

- 最大96セグメント

- 可変クロック入力

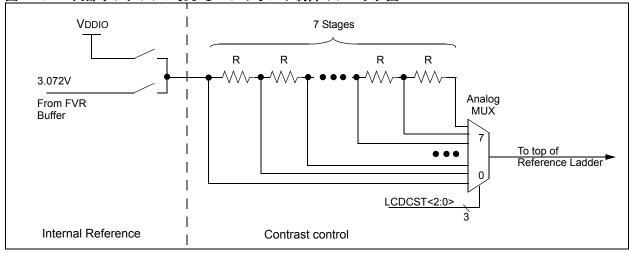

- コントラスト制御

- 内部電圧リファレンスのセレクション

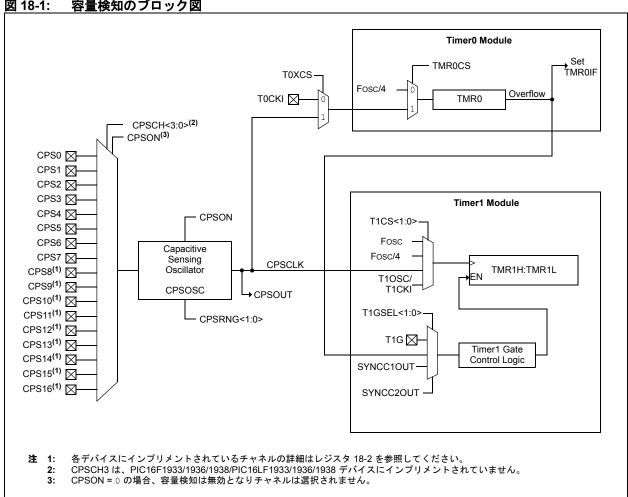

- ・ 容量検知モジュール (mTouch™)

- 最大16本の選択可能チャネル

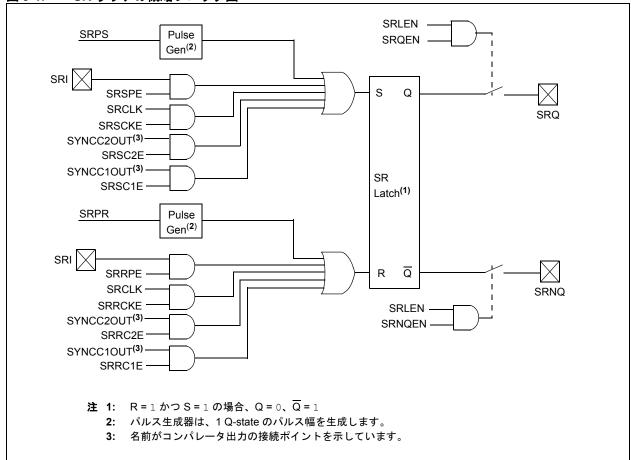

- A/D コンバータ:

- 10 ビット分解能および最大 14 チャネル

- 選択可能な電圧リファレンス (1.024/2.048/4.096V)

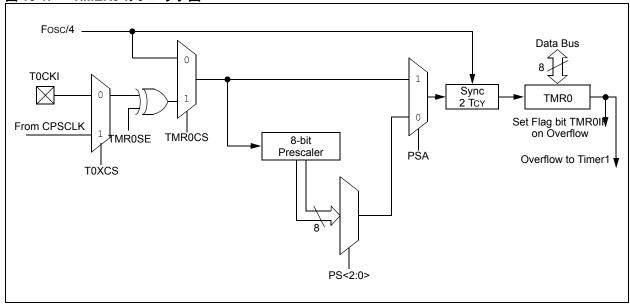

- Timer0: 8 ビット プログラマブル プリスケーラ付 き8ビットタイマ/カウンタ

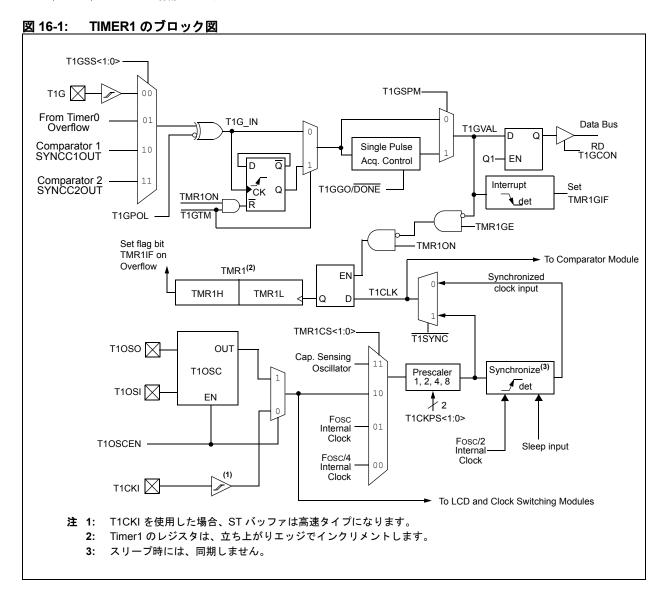

- · 拡張 Timer1:

- 専用の低電力 32 kHz オシレータ ドライバ

- プリスケーラ付き 16 ビット タイマ / カウンタ

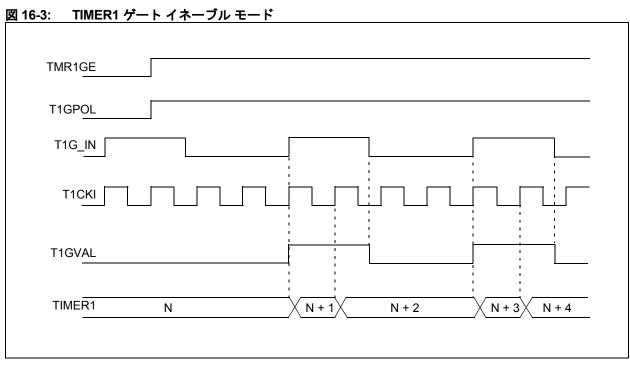

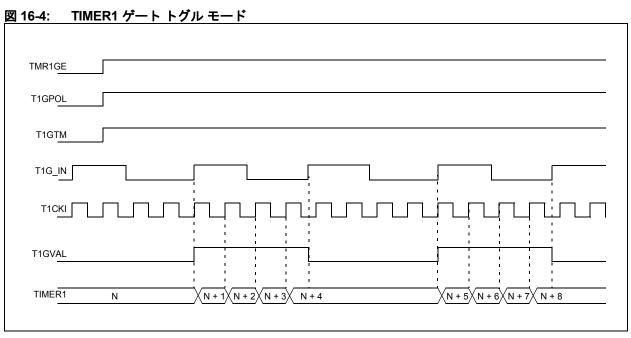

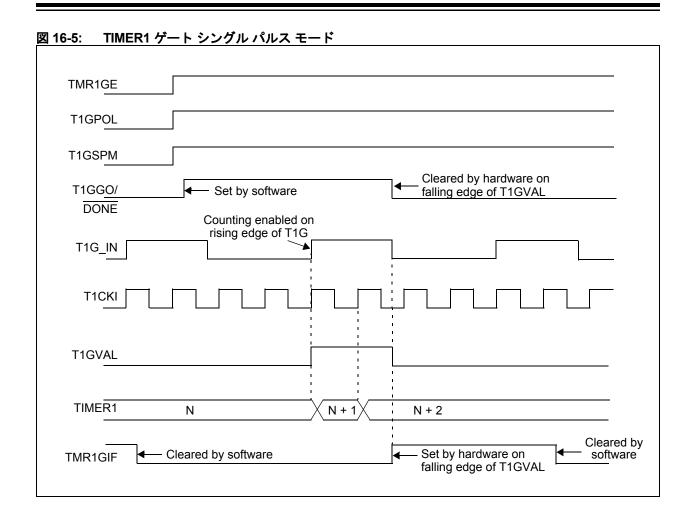

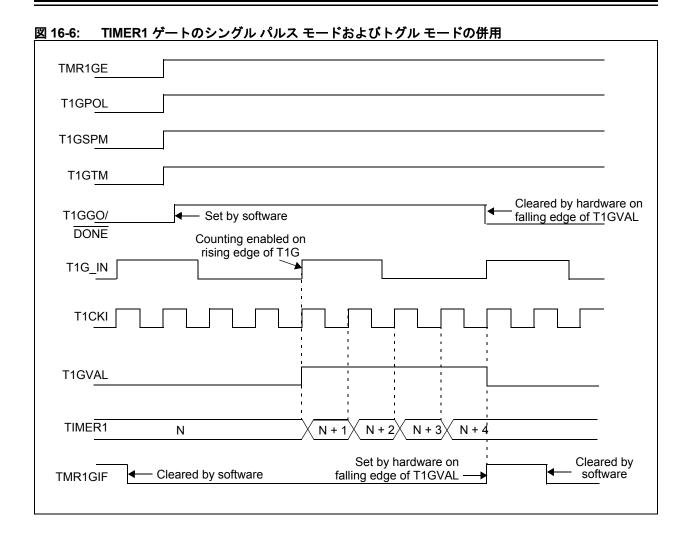

- トグル付きの外部ゲート入力モードおよび シングル ショットモード

- ゲートイベント完了時の割り込み

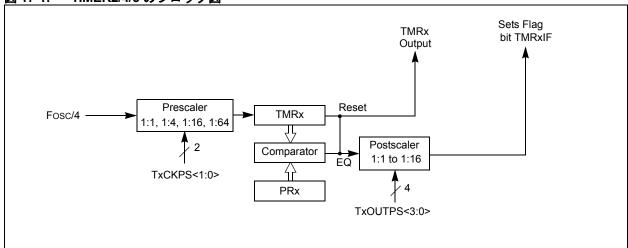

- Timer2、4、6:8ビット周期レジスタ、プリス ケーラおよびポストスケーラ付き8ビットタイ マ/カウンタ

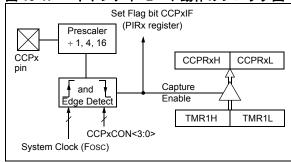

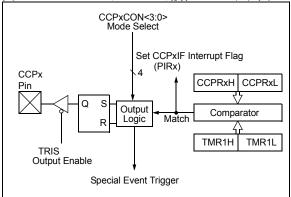

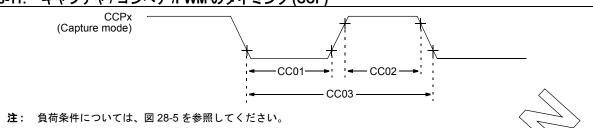

- 2つのキャプチャ、コンペア、PWM モジュール (CCP)

- 16 ビットキャプチャ、最大分解能 125 ns

- 16 ビットコンペア、最大分解能 125 ns

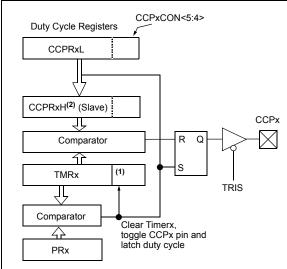

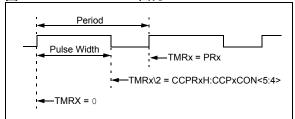

- 10 ビット PWM、最大周波数 31.25 kHz

- 3 つの拡張キャプチャ / コンペア /PWM (ECCP) モジュール:

- 3 つの PWM タイム ベース オプション

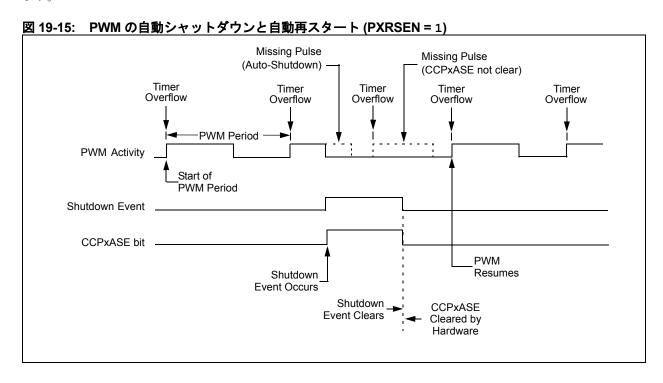

- 自動シャットダウンおよび自動再スタート

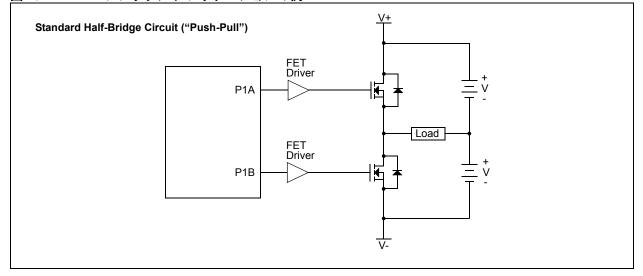

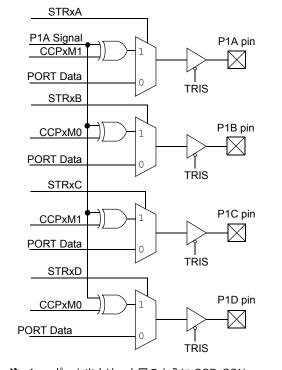

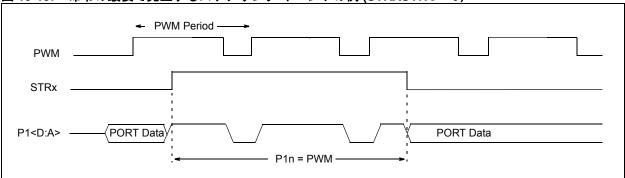

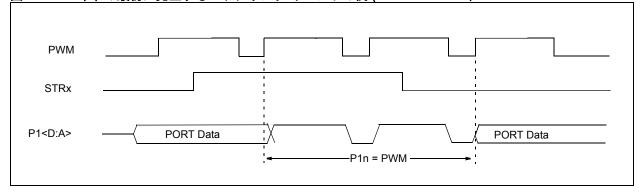

- PWM ステアリング

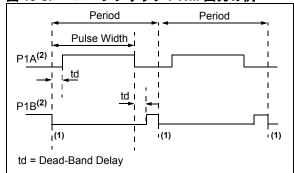

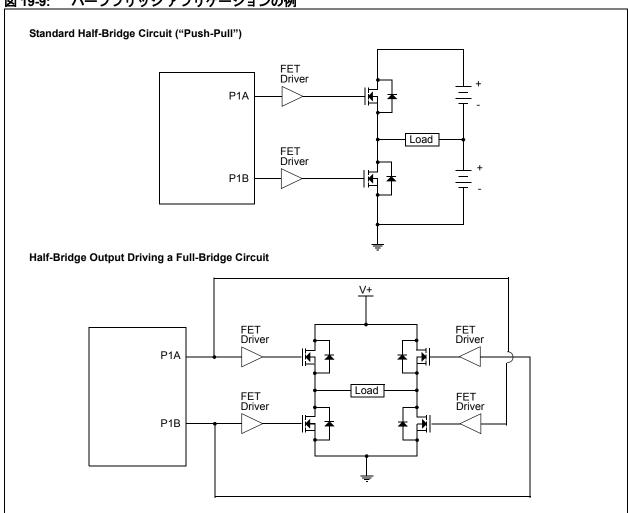

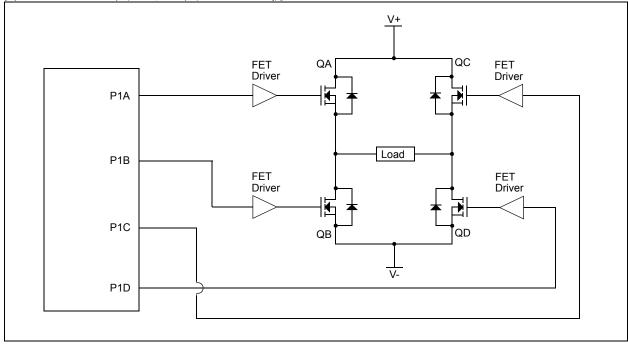

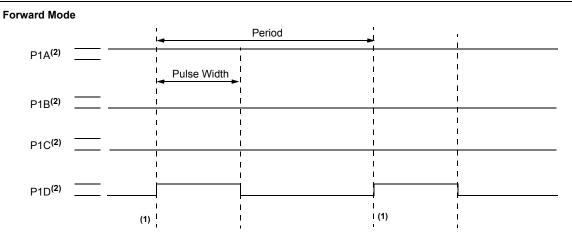

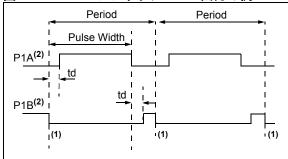

- プログラマブルなデッドバンド遅延

#### 周辺機能の特徴 (続き):

- SPI および I<sup>2</sup>CTM を備えた MSSP (Master Synchronous Serial Port):

- 7ビットのアドレスマスキング

- SMBUS/PMBUS™ と互換性あり

- スタート時に自動ウェイクアップ

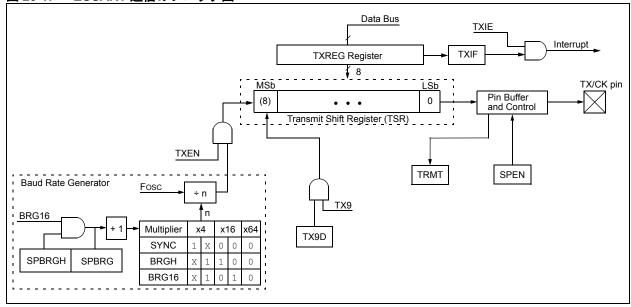

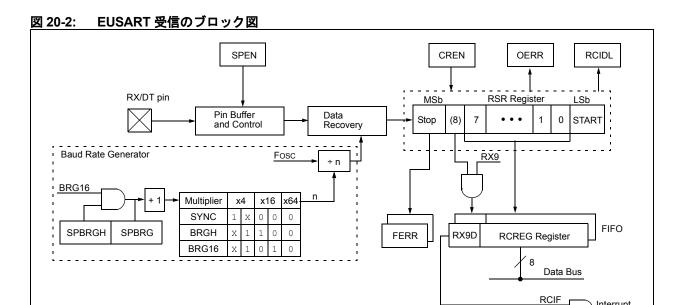

- EUSART (Enhanced Universal Synchronous Asynchronous Receiver Transmitter)

- RS-232、RS 485 および LIN と互換性あり

- 自動ボーレート検出

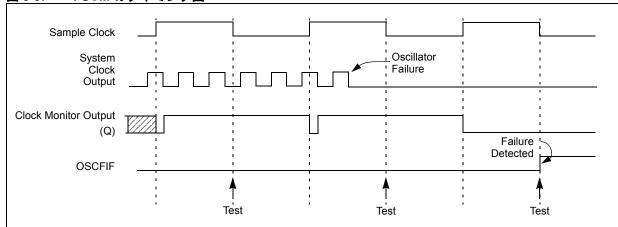

- SR ラッチ (555 タイマ):

- 複数のセット/リセット入力オプション

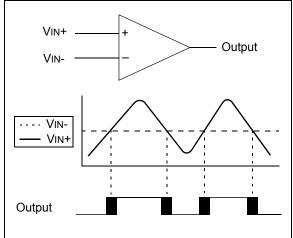

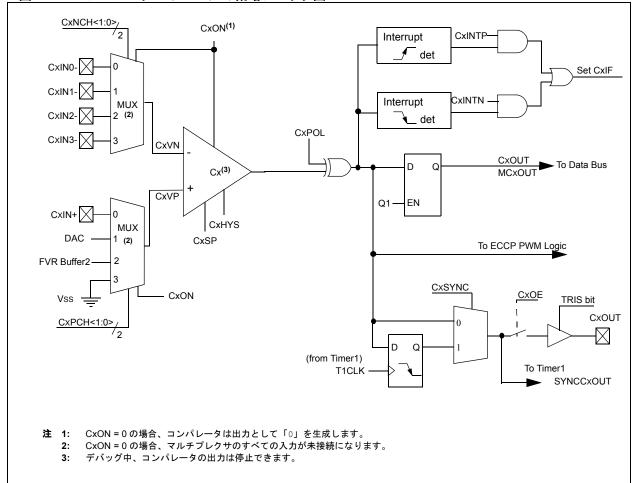

- 2個のコンパレータ:

- レールツーレール入力/出力

- 電源モード制御

- ソフトウェアによるヒステリシスの有効化

- 電圧リファレンス モジュール:

- 固定電圧リファレンス (FVR) 出力レベルは 1.024V、2.048V および 4.096V

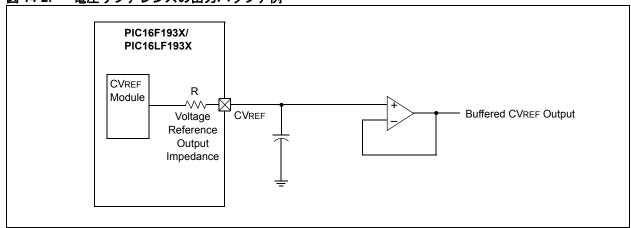

- 反転 / 非反転を選択可能な 5 ビットのレール ツー レールの抵抗ストリング型 DAC

#### PIC16F193X/LF193X ファミリの種類

| デバイス                      | プログラム メモリ<br>フラッシュ (ワード) | データ EEPROM<br>(パイト) | SRAM (バイト) | 0 数 | 10 ピット A/D<br>(ch) | 容量検知<br>(ch) | ターつパンロ | タイマ<br>8/16 ビット | EUSART | l²C™/SPI | ECCP | CCP | ГСБ                  |

|---------------------------|--------------------------|---------------------|------------|-----|--------------------|--------------|--------|-----------------|--------|----------|------|-----|----------------------|

| PIC16F1933<br>PIC16LF1933 | 4096                     | 256                 | 256        | 25  | 11                 | 8            | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 16 <sup>(1)</sup> /4 |

| PIC16F1934<br>PIC16LF1934 | 4096                     | 256                 | 256        | 36  | 14                 | 16           | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 24/4                 |

| PIC16F1936<br>PIC16LF1936 | 8192                     | 256                 | 512        | 25  | 11                 | 8            | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 16 <sup>(1)</sup> /4 |

| PIC16F1937<br>PIC16LF1937 | 8192                     | 256                 | 512        | 36  | 14                 | 16           | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 24/4                 |

| PIC16F1938<br>PIC16LF1938 | 16384                    | 256                 | 1024       | 25  | 11                 | 8            | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 16 <sup>(1)</sup> /4 |

| PIC16F1939<br>PIC16LF1939 | 16384                    | 256                 | 1024       | 36  | 14                 | 16           | 2      | 4/1             | Yes    | Yes      | 3    | 2   | 24/4                 |

**注 1:** PIC16F1933/1936/1938/PIC16LF1933/1936/1938 では、COM3 と SEG15 が同じピンを使用するため、1/4 マルチプレクス ディスプレイを使用する場合、SEG15 は使用できません。

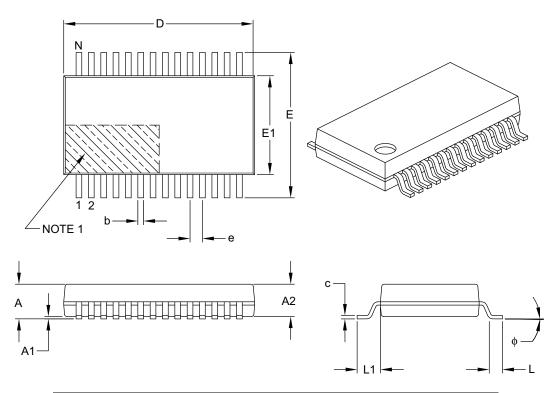

#### ピン配置図 — 28 ピン SPDIP/SOIC/SSOP (PIC16F1933/19<u>36/1938、PIC16LF1933/1936/1938)</u> 28 ピン SPDIP、SOIC、SSOP Vpp/MCLR/RE3 —► 1 28 → RB7/ICSPDAT/ICDDAT/SEG13 27 → RB6/ICSPCLK/ICDCLK/SEG14 SEG12/VCAP<sup>(2)</sup>/ $\overline{SS}^{(1)}$ /SRNQ<sup>(1)</sup>/C2OUT<sup>(1)</sup>/C12IN0-/AN0/RA0 $\rightarrow$ 26 RB5/AN13/CPS5/P2B<sup>(1)</sup>/CCP3<sup>(1)</sup>/P3A<sup>(1)</sup>/T1G<sup>(1)</sup>/COM1 SEG7/C12IN1-/AN1/RA1 → 3 25 RB4/AN11/CPS4/P1D/COM0 COM2/DACOUT/VREF-/C2IN+/AN2/RA2 → 4 24 T RB3/AN9/C12IN2-/CPS3/CCP2<sup>(1)</sup>/P2A<sup>(1)</sup>/VLCD3 SEG15/COM3/VREF+/C1IN+/AN3/RA3 → 5 23 → RB2/AN8/CPS2/P1B/VLCD2 SEG4/CCP5/SRQ/T0CKI/CPS6/C1OUT/RA4 →► 6 22 → RB1/AN10/C12IN3-/CPS1/P1C/VLCD1 SEG5/Vcap<sup>(2)</sup>/SS<sup>(1)</sup>/SRNQ<sup>(1)</sup>/CPS7/C2OUT<sup>(1)</sup>/AN4/RA5 → 7 21 ☐ ← RB0/AN12/CPS0/CCP4/SRI/INT/SEG0 20 **→** VDD SEG2/CLKIN/OSC1/RA7 → 9 19 **→** Vss SEG1/Vcap<sup>(2)</sup>/CLKOUT/OSC2/RA6 → 10 18 → RC7/RX/DT/P3B/SEG8 P2B<sup>(1)</sup>/T1CKI/T1OSO/RC0 → 11 17 → RC6/TX/CK/CCP3<sup>(1)</sup>/P3A<sup>(1)</sup>/SEG9 P2A<sup>(1)</sup>/CCP2<sup>(1)</sup>/T1OSI/RC1 → 12 16 RC5/SDO/SEG10 SEG3/P1A/CCP1/RC2 ←►☐ 13 15 → RC4/SDI/SDA/T1G<sup>(1)</sup>/SEG11 SEG6/SCL/SCK/RC3 → 14 注 1: APFCON レジスタを介してピン機能を選択できます。

PIC16F193X デバイスのみ。

© 2009 Microchip Technology Inc. **Preliminary** DS41364B\_JP - ページ 3

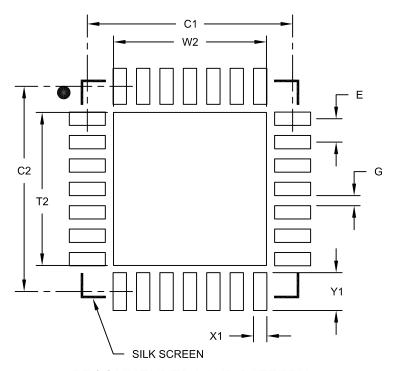

### ピン配置図 — 28 ピン QFN (PIC16F1933/1936/1938、PIC16LF1933/1936/1938) 28 ピン QFN RA0/AN0/C12IN0-/C2OUT(1)/SRNQ(1)/SS(1)/VCAP(2)/SEG12 RB5/AN13/CPS5/P2B<sup>(1)</sup>/CCP3<sup>(1)</sup>/P3A<sup>(1)</sup>/T1G<sup>(1)</sup>/COM1 RB7/ICSPDAT/ICDDAT/SEG13 RB4/AN11/CPS4/P1D/COM0 RA1/AN1/C12IN1-/SEG7 28 27 26 25 25 23 23 23 COM2/DACOUT/VREF-/C2IN+/AN2/RA2 ◆→ ← RB3/AN9/C12IN2-/CPS3/CCP2<sup>(1)</sup>/P2A<sup>(1)</sup>/VLCD3 RB2/AN8/CPS2/P1B/VLCD2 SEG15/COM3/VREF+/C1IN+/AN3/RA3 → 2 SEG4/CCP5/SRQ/T0CKI/CPS6/C1OUT/RA4 -> 3 PIC16F1933/1936/1938 19 I SEG5<sup>(1)</sup>/VCAP<sup>(2)</sup>/ $\overline{SS}^{(1)}$ /SRNQ/CPS7/C2OUT<sup>(1)</sup>/AN4/RA5 $\Leftrightarrow$ → RB0/AN12/CPS0/CCP4/SRI/INT/SEG0 <sup>4</sup> PIC16LF1933/1936/1938 <sup>18</sup> 17 **←** Vdd SEG2/CLKIN/OSC1/RA7 6 **⊸**Vss 16 SEG1/VCAP<sup>(2)</sup>/CLKOUT/OSC2/RA6 → 7 RC7/RX/DT/P3B/SEG8 15 P2B(1)/T1CKI/T10SO/RC0 SEG6/SCL/SCK/RC3 SEG11/T1G<sup>(1)</sup>/SDA/SDI/RC4 SEG9/P3A(1)/CCP3(1)/CK/TX/RC6 SEG3/P1A/CCP1/RC2

APFCON レジスタを介してピン機能を選択できます。

PIC16F193X デバイスのみ。

28 ピンの要約 (PIC16F1933/1936/1938、PIC16LF1933/1936/1938) 表 1:

|     | SIP      | N         |       | · · ·         | ,    | *                                | *                   |                    |                                                                   | <b>–</b> | ,                 |                | 4           | ٦    |                                        |

|-----|----------|-----------|-------|---------------|------|----------------------------------|---------------------|--------------------|-------------------------------------------------------------------|----------|-------------------|----------------|-------------|------|----------------------------------------|

| O/I | 28 ピンS   | 28 ピン QFN | ANSEL | A/D           | 容量検知 | コンパレー                            | SRラッチ               | 912                | CCP                                                               | EUSART   | MSSP              | CCD            | 割り込み        | プルアッ | 増                                      |

| RA0 | 2        | 27        | Y     | AN0           | 1    | C12IN0-/C<br>2OUT <sup>(1)</sup> | SRNQ <sup>(1)</sup> |                    |                                                                   | _        | <u>SS</u> (1)     | SEG12          |             |      | VCAP <sup>(2)</sup>                    |

| RA1 | 3        | 28        | Y     | AN1           | _    | C12IN1-                          | _                   | _                  | _                                                                 | _        | _                 | SEG7           | _           | _    | _                                      |

| RA2 | 4        | 1         | Y     | AN2/<br>Vref- | _    | C2IN+/<br>DACOUT                 | _                   | _                  | _                                                                 | _        | _                 | COM2           | _           | _    | _                                      |

| RA3 | 5        | 2         | Y     | AN3/<br>VREF+ | _    | C1IN+                            | _                   | _                  | _                                                                 | _        | _                 | SEG15/C<br>OM3 | _           |      | _                                      |

| RA4 | 6        | 3         | Y     | _             | CPS6 | C1OUT                            | SRQ                 | T0CKI              | CCP5                                                              | _        | _                 | SEG4           | _           | _    | _                                      |

| RA5 | 7        | 4         | Y     | AN4           | CPS7 | C2OUT <sup>(1)</sup>             | SRNQ <sup>(1)</sup> | _                  |                                                                   | _        | SS <sup>(1)</sup> | SEG5           | _           |      | VCAP <sup>(2)</sup>                    |

| RA6 | 10       | 7         | _     |               |      |                                  |                     |                    | _                                                                 | _        | 1                 | SEG1           |             |      | OSC2/<br>CLKOUT<br>VCAP <sup>(2)</sup> |

| RA7 | 9        | 6         |       |               |      |                                  |                     |                    | _                                                                 |          |                   | SEG2           |             |      | OSC1/<br>CLKIN                         |

| RB0 | 21       | 18        | Y     | AN12          | CPS0 | _                                | SRI                 | _                  | CCP4                                                              | _        | _                 | SEG0           | INT/<br>IOC | Y    | _                                      |

| RB1 | 22       | 19        | Y     | AN10          | CPS1 | C12IN3-                          |                     | _                  | P1C                                                               | _        | 1                 | VLCD1          | IOC         | Y    | _                                      |

| RB2 | 23       | 20        | Y     | AN8           | CPS2 | _                                | _                   | _                  | P1B                                                               | _        | _                 | VLCD2          | IOC         | Y    | _                                      |

| RB3 | 24       | 21        | Y     | AN9           | CPS3 | C12IN2-                          | _                   | _                  | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup>                       | _        | _                 | VLCD3          | IOC         | Y    | _                                      |

| RB4 | 25       | 22        | Y     | AN11          | CPS4 | _                                | _                   | _                  | P1D                                                               | _        | _                 | COM0           | IOC         | Y    | _                                      |

| RB5 | 26       | 23        | Y     | AN13          | CPS5 |                                  | ĺ                   | T1G <sup>(1)</sup> | P2B <sup>(1)</sup><br>CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> |          | ĺ                 | COM1           | IOC         | Y    |                                        |

| RB6 | 27       | 24        | _     | I             | 1    | 1                                | 1                   | 1                  |                                                                   | _        | 1                 | SEG14          | IOC         | Y    | ICSPCLK/<br>ICDCLK                     |

| RB7 | 28       | 25        |       |               |      |                                  |                     |                    | _                                                                 |          |                   | SEG13          | IOC         | Y    | ICSPDAT/<br>ICDDAT                     |

| RC0 | 11       | 8         |       | _             | _    | _                                | _                   | T1OSO/<br>T1CKI    | P2B <sup>(1)</sup>                                                | _        | _                 | _              |             |      | _                                      |

| RC1 | 12       | 9         |       |               |      |                                  |                     | TIOSI              | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup>                       |          |                   | _              |             |      |                                        |

| RC2 | 13       | 10        |       | _             | _    | _                                | _                   | _                  | CCP1/<br>P1A                                                      |          | _                 | SEG3           |             |      | _                                      |

| RC3 | 14       | 11        | _     | 1             | _    | _                                | _                   | _                  | _                                                                 | _        | SCK/SCL           | SEG6           | _           | 1    | _                                      |

| RC4 | 15       | 12        | _     | _             |      |                                  |                     | T1G <sup>(1)</sup> | _                                                                 |          | SDI/SDA           | SEG11          |             | _    | _                                      |

| RC5 | 16       | 13        | _     | _             | _    | _                                | _                   | _                  | _                                                                 |          | SDO               | SEG10          | _           | _    | _                                      |

| RC6 | 17       | 14        |       | ı             | ı    | ı                                | _                   | ı                  | CCP3 <sup>(1)</sup><br>P3A <sup>(1)</sup>                         | TX/CK    | ı                 | SEG9           |             | 1    | _                                      |

| RC7 | 18       | 15        | _     | _             | _    | _                                | _                   | _                  | P3B                                                               | RX/DT    | _                 | SEG8           | _           |      |                                        |

| RE3 | 1        | 26        | _     | _             | _    | _                                | _                   | _                  | _                                                                 | _        | _                 | _              | _           | Y    | MCLR/VPP                               |

| VDD | 20       | 17        | _     | _             | _    | _                                | _                   | _                  | _                                                                 | _        | _                 | _              | _           | _    | Vdd                                    |

| Vss | 8,<br>19 | 5,<br>16  | _     |               |      |                                  | ĺ                   |                    | _                                                                 | _        | _                 | _              | _           |      | Vss                                    |

APECON レジスタを使用してピン機能を移動できます。 PIC16F193X デバイスのみ。 注 1:

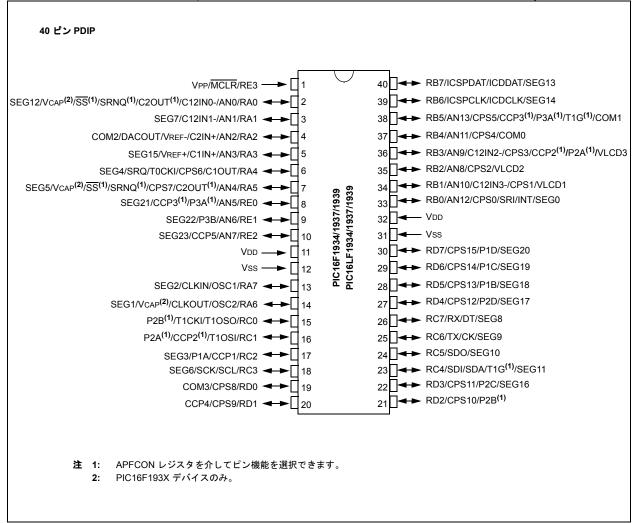

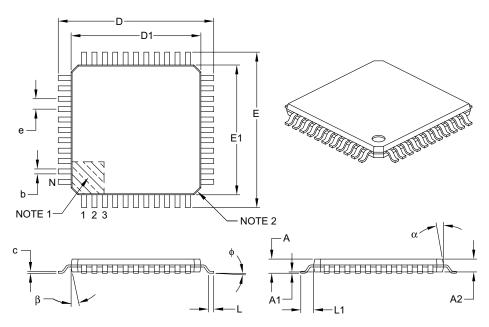

#### ピン配置図 — 40 ピン PDIP (PIC16F1934/1937/1939、PIC16LF1934/1937/1939)

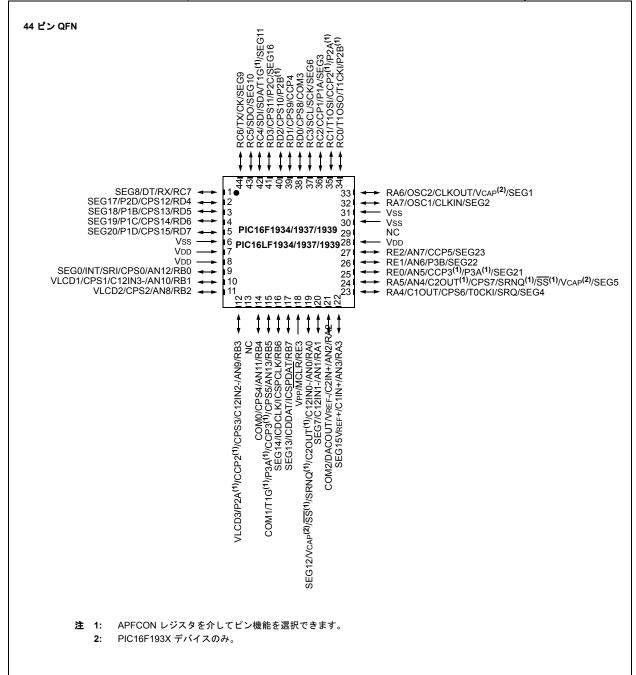

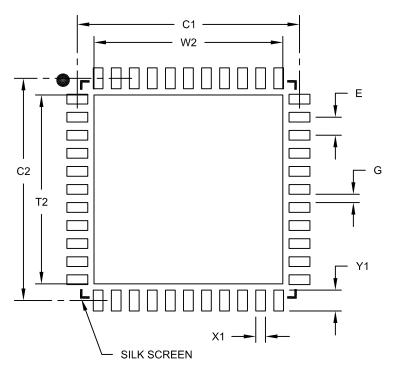

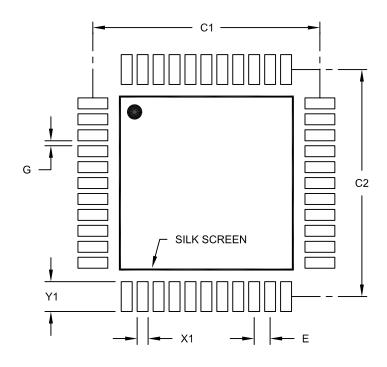

#### ピン配置図 — 44 ピン QFN (PIC16F1934/1937/1939、PIC16LF1934/1937/1939)

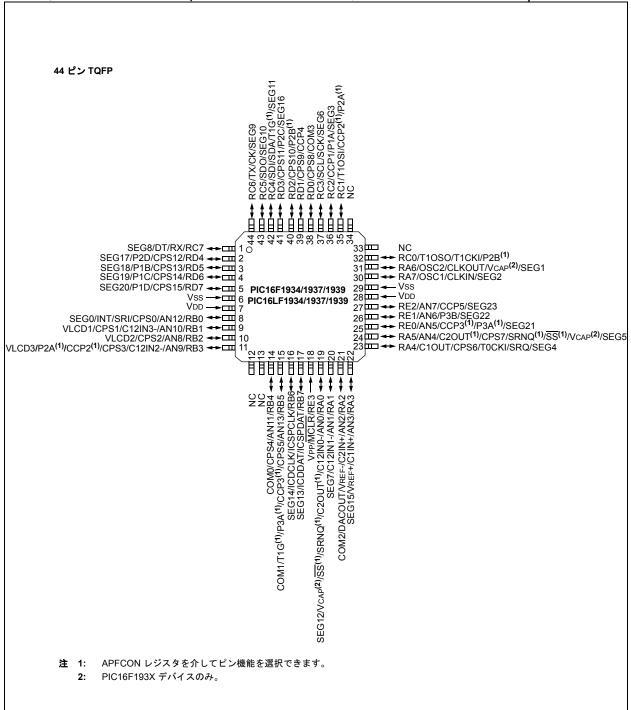

#### ピン配置図 — 44 ピン TQFP (PIC16F1934/1937/1939、PIC16LF1934/1937/1939)

表 2: 40/44 ピンの要約 (PIC16F1934/1937/1939、PIC16LF1934/1937/1939)

| 衣 4: |            |            | דע יעד      | ·     | リン女小:         | , (1 10 1 | 01 1337/                         | 1331113             | <u>55, 110</u>     | JIOLF 19                                    | <del>737/13</del> 0 | ,,,,,,,,,         |       |             |       |                         |

|------|------------|------------|-------------|-------|---------------|-----------|----------------------------------|---------------------|--------------------|---------------------------------------------|---------------------|-------------------|-------|-------------|-------|-------------------------|

| 0/1  | 40 ピン PDIP | 44 ピン TQFP | 44 ピン QFN   | ANSEL | A/D           | 容量検知      | キーつかくロ                           | SRラッチ               | タイマ                | CCP                                         | EUSART              | MSSP              | ГСР   | 割り込み        | プルアップ | 業本                      |

| RA0  | 2          | 19         | 19          | Y     | AN0           | _         | C12IN0-/C<br>2OUT <sup>(1)</sup> | SRNQ <sup>(1)</sup> | _                  | _                                           | _                   | <u>SS</u> (1)     | SEG12 | _           | _     | VCAP                    |

| RA1  | 3          | 20         | 20          | Y     | AN1           |           | C12IN1-                          | _                   | _                  | _                                           |                     | _                 | SEG7  | _           | _     | _                       |

| RA2  | 4          | 21         | 21          | Y     | AN2/<br>VREF- | _         | C2IN+/<br>DACOUT                 | _                   | _                  | _                                           | _                   | _                 | COM2  | _           | _     | _                       |

| RA3  | 5          | 22         | 22          | Y     | AN3/<br>VREF+ | 1         | C1IN+                            | _                   | _                  | _                                           | _                   | _                 | SEG15 | _           | _     | _                       |

| RA4  | 6          | 23         | 23          | Y     | _             | CPS6      | C1OUT                            | SRQ                 | T0CKI              |                                             | _                   | _                 | SEG4  | _           | _     | _                       |

| RA5  | 7          | 24         | 24          | Y     | AN4           | CPS7      | C2OUT <sup>(1)</sup>             | SRNQ <sup>(1)</sup> | _                  | _                                           | _                   | SS <sup>(1)</sup> | SEG5  | _           | _     | VCAP                    |

| RA6  | 14         | 31         | 33          | _     |               | _         | _                                | _                   | _                  | _                                           | _                   | _                 | SEG1  | _           | _     | OSC2/<br>CLKOUT<br>VCAP |

| RA7  | 13         | 30         | 32          | _     | _             |           | _                                | _                   | _                  | _                                           | _                   | _                 | SEG2  | _           | ĺ     | OSC1/<br>CLKIN          |

| RB0  | 33         | 8          | 9           | Y     | AN12          | CPS0      | _                                | SRI                 | _                  | _                                           | _                   | _                 | SEG0  | INT/<br>IOC | Y     |                         |

| RB1  | 34         | 9          | 10          | Y     | AN10          | CPS1      | C12IN3-                          | _                   | _                  | _                                           | _                   | _                 | VLCD1 | IOC         | Y     | _                       |

| RB2  | 35         | 10         | 11          | Y     | AN8           | CPS2      | _                                | _                   | _                  | _                                           | _                   | _                 | VLCD2 | IOC         | Y     | _                       |

| RB3  | 36         | 11         | 12          | Y     | AN9           | CPS3      | C12IN2-                          | _                   | _                  | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup> | _                   | _                 | VLCD3 | IOC         | Y     | _                       |

| RB4  | 37         | 14         | 14          | Y     | AN11          | CPS4      | _                                | _                   | _                  | _                                           | _                   | _                 | COM0  | IOC         | Y     | _                       |

| RB5  | 38         | 15         | 15          | Y     | AN13          | CPS5      | _                                | _                   | T1G <sup>(1)</sup> | CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> | _                   | _                 | COM1  | IOC         | Y     | _                       |

| RB6  | 39         | 16         | 16          | _     | _             | _         | _                                | _                   | _                  | _                                           | _                   | _                 | SEG14 | IOC         | Y     | ICSPCLK/<br>ICDCLK      |

| RB7  | 40         | 17         | 17          | _     |               | _         | _                                | _                   | _                  | _                                           | _                   | _                 | SEG13 | IOC         | Y     | ICSPDAT/<br>ICDDAT      |

| RC0  | 15         | 32         | 34          | _     | _             | _         | _                                | _                   | T1OSO/<br>T1CKI    | P2B <sup>(1)</sup>                          | _                   | _                 | _     | _           | _     | _                       |

| RC1  | 16         | 35         | 35          | _     | _             | _         | _                                | _                   | TIOSI              | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup> | _                   | _                 | _     | _           | _     | _                       |

| RC2  | 17         | 36         | 36          | _     | _             | _         | _                                | _                   | _                  | CCP1/<br>P1A                                | _                   | _                 | SEG3  | _           | _     | _                       |

| RC3  | 18         | 37         | 37          | _     | _             | _         | _                                | _                   | _                  | _                                           | _                   | SCK/SCL           | SEG6  | _           | _     | _                       |

| RC4  | 23         | 42         | 42          | _     | _             | _         | _                                | _                   | T1G <sup>(1)</sup> | _                                           | _                   | SDI/SDA           | SEG11 | _           | _     | _                       |

| RC5  | 24         | 43         | 43          | _     | _             | _         | _                                | _                   | _                  | _                                           | _                   | SDO               | SEG10 | _           | _     | _                       |

| RC6  | 25         | 44         | 44          | _     | _             | _         | _                                | _                   | _                  | _                                           | TX/CK               | _                 | SEG9  | _           | _     | _                       |

| RC7  | 26         | 1          | 1           |       | _             |           | _                                | _                   | _                  | _                                           | RX/DT               | _                 | SEG8  | _           | _     | _                       |

| RD0  | 19         | 38         | 38          | Y     | _             | CPS8      | _                                | _                   | _                  | _                                           |                     | _                 | COM3  | _           | _     | _                       |

| RD1  | 20         | 39         | 39          | Y     |               | CPS9      | _                                | _                   | _                  | CCP4                                        | _                   | _                 | _     | _           | _     | _                       |

| RD2  | 21         | 40         | 40          | Y     | —             | CPS10     | _                                | _                   | _                  | P2B <sup>(1)</sup>                          | _                   | _                 | _     | _           | _     | _                       |

| RD3  | 22         | 41         | 41          | Y     | _             | CPS11     | _                                | _                   | _                  | P2C                                         | _                   | _                 | SEG16 |             |       | _                       |

| RD4  | 27         | 2          | 2           | Y     | _             | CPS12     | _                                | _                   | _                  | P2D                                         | _                   | _                 | SEG17 | _           | _     | _                       |

| RD5  | 28         | 3          | 3           | Y     | _             | CPS13     | _                                | _                   | _                  | P1B                                         |                     | _                 | SEG18 |             | _     | _                       |

| RD6  | 29         | 4          | 4           | Y     | _             | CPS14     | _                                | _                   | _                  | P1C                                         | _                   | _                 | SEG19 | _           | _     | _                       |

| RD7  | 30         | 5          | 5           | Y     | —<br>ANG      | CPS15     |                                  |                     | _                  | P1D<br>CCP3 <sup>(1)</sup>                  |                     | _                 | SEG20 |             |       | _                       |

| RE0  | 8          | 25         | 25          | Y     | AN5           | _         | _                                | _                   | _                  | P3A <sup>(1)</sup>                          |                     | _                 | SEG21 | _           |       | _                       |

| RE1  | 9          | 26         | 26          | Y     | AN6           |           |                                  |                     | _                  | P3B                                         |                     | _                 | SEG22 | _           |       | _                       |

| RE2  | 10         | 27         | 27          | Y     | AN7           |           |                                  | _                   | _                  | CCP5                                        |                     |                   | SEG23 | _           | _     |                         |

| RE3  | 1 11,      | 18<br>7,2  | 18<br>7,8,  | _     | _             | _         | _                                | _                   | _                  | _                                           | _                   | _                 |       | _           | Y —   | MCLR/VPP<br>VDD         |

| Vss  | 32<br>12,  | 6,2        | 28<br>6,30, | _     |               | _         | _                                | _                   | _                  | _                                           | _                   | _                 | _     | _           | _     | Vss                     |

| . 55 | 31         | 9          | 31          |       |               |           |                                  |                     |                    |                                             |                     |                   |       |             |       |                         |

注 1: APECON レジスタを使用してピン機能を移動できます。

### 目次

| 1.0  | デバイス概要                                                                    | 13  |

|------|---------------------------------------------------------------------------|-----|

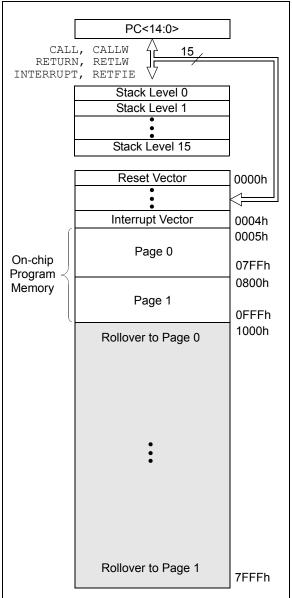

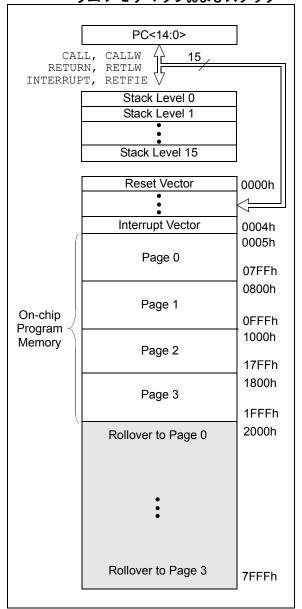

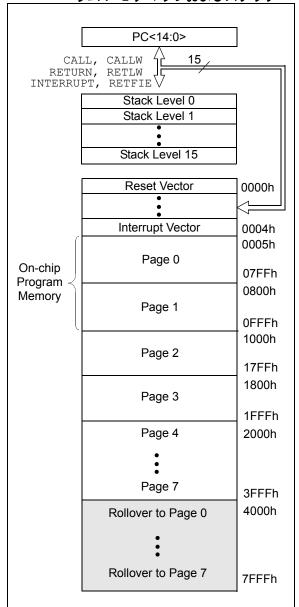

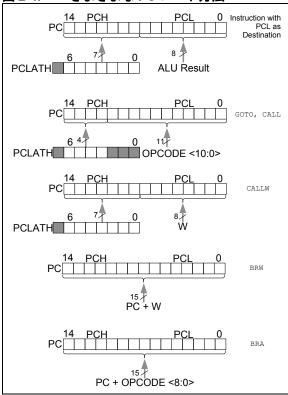

| 2.0  | メモリ構成                                                                     | 21  |

| 3.0  | リセット                                                                      | 57  |

| 4.0  | 割り込み                                                                      | 69  |

| 5.0  | 低ドロップアウト (LDO) 電圧レギュレータ                                                   | 81  |

| 6.0  | 1/0 ポート                                                                   |     |

| 7.0  | 状態変化割り込み                                                                  | 103 |

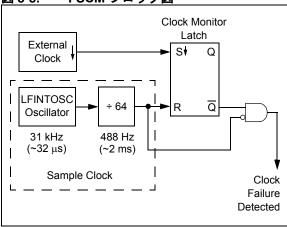

| 8.0  | オシレータ モジュール (フェイルセーフ クロック モニタ機能付き )                                       | 107 |

| 9.0  | SR ラッチ                                                                    |     |

| 10.0 | デバイス コンフィギュレーション                                                          | 125 |

| 11.0 | A/D 変換 (ADC) モジュール                                                        |     |

|      | コンパレータ モジュール                                                              |     |

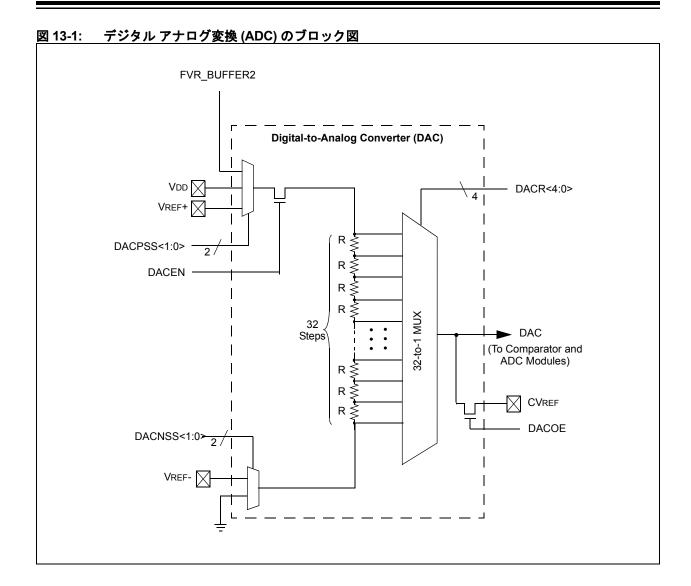

| 13.0 | デジタル アナログ変換 (DAC) モジュール                                                   | 151 |

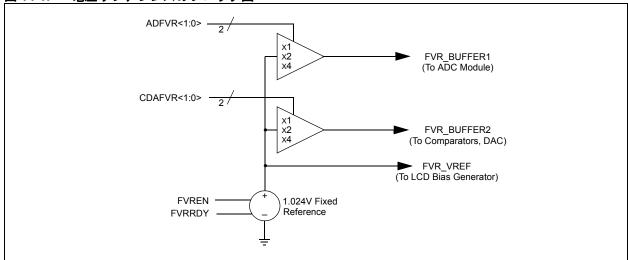

| 14.0 | 固定電圧リファレンス                                                                | 155 |

| 15.0 | Timer0 モジュール                                                              | 157 |

| 16.0 | Timer1 モジュール (ゲート制御対応 )                                                   | 161 |

| 17.0 | Timer 2、4、6 モジュール                                                         | 173 |

| 18.0 | 容量検知モジュール                                                                 |     |

| 19.0 | キャプチャ/コンペア/PWM モジュール (ECCP1、ECCP2、ECCP3、CCP4、CCP5)                        | 183 |

|      | EUSART (Enhanced Universal Synchronous Asynchronous Receiver Transmitter) |     |

|      | 液晶ディスプレイ (LCD) ドライバ モジュール                                                 |     |

| 22.0 | マスター同期シリアル ポート (MSSP) モジュール                                               | 273 |

|      | データ EEPROM およびフラッシュ プログラム メモリ制御                                           |     |

| 24.0 | パワーダウン モード (スリープ)                                                         | 333 |

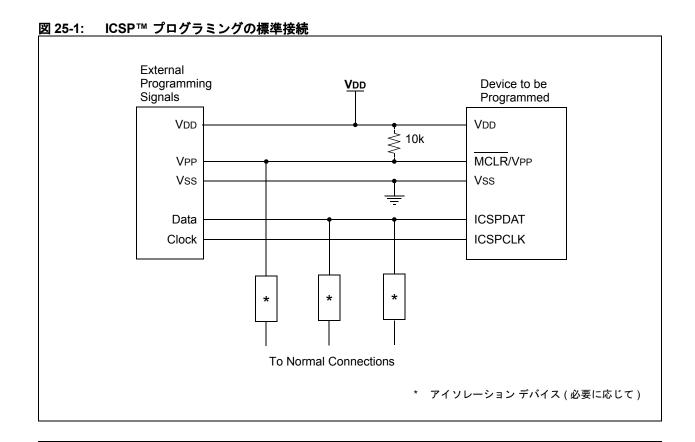

| 25.0 | In-Circuit Serial Programming <sup>TM</sup> (ICSP <sup>TM</sup> )         | 335 |

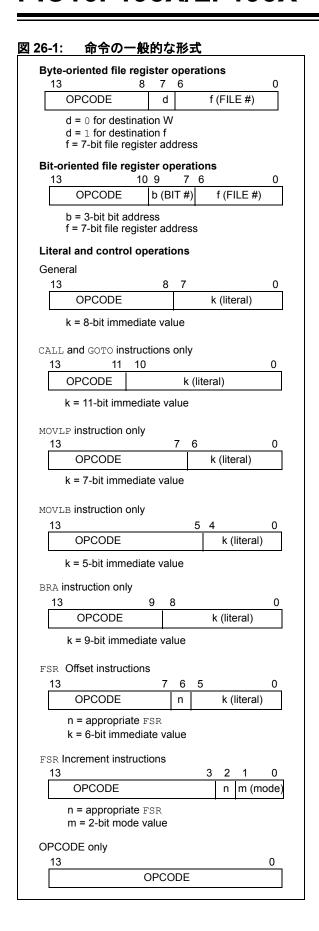

| 26.0 | 命令セットのまとめ                                                                 | 337 |

| 27.0 | 開発サポート                                                                    | 351 |

| 28.0 | 電気的仕様                                                                     | 355 |

|      | DC および AC 特性の図 / 表                                                        |     |

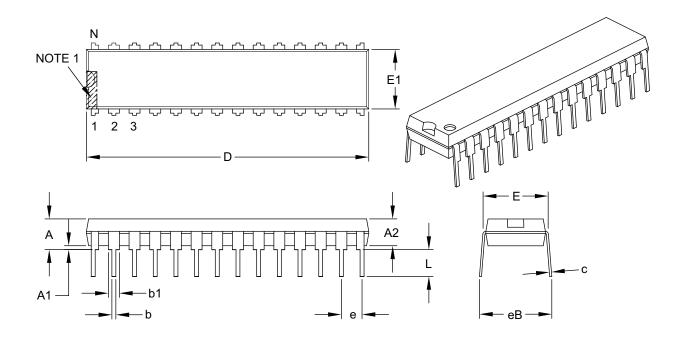

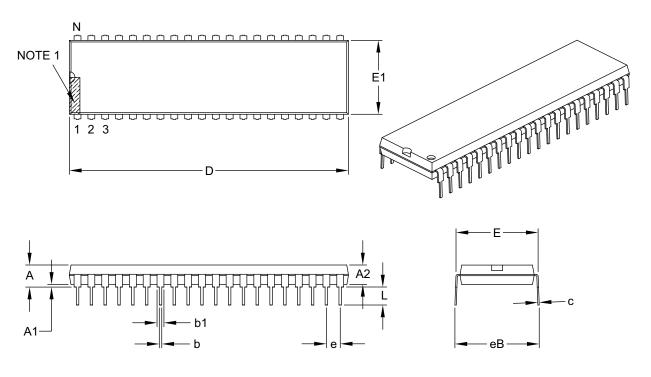

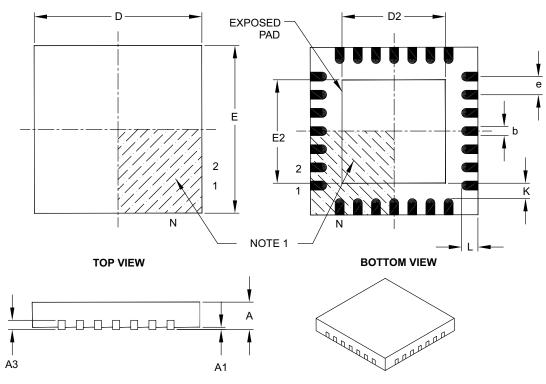

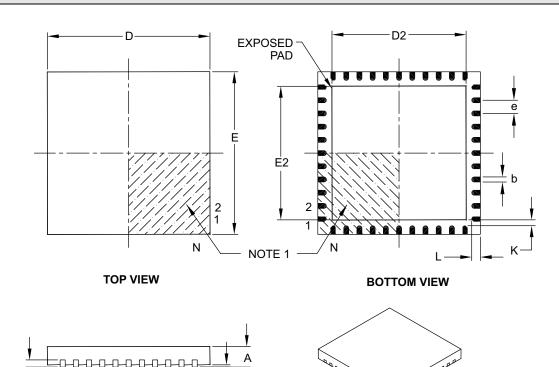

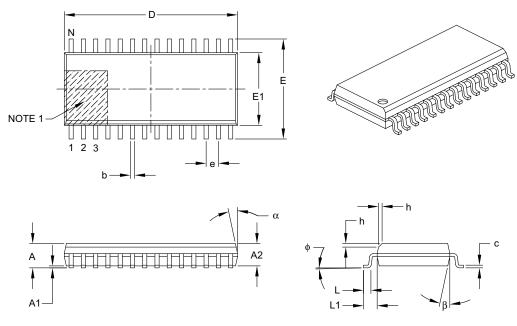

| 30.0 | パッケージ情報                                                                   | 391 |

| 付録   | A: データシート改版履歴                                                             | 403 |

|      | B: 他の PIC® デバイスからの移行                                                      |     |

| 索引   |                                                                           | 405 |

| マイ   | クロチップ社のウェブ サイト                                                            | 413 |

| お客   | 様への変更通知サービス                                                               | 413 |

| お客   | 様サポート                                                                     | 413 |

| 読者   | アンケート                                                                     | 414 |

| 制旦   | 禁則システム                                                                    | 415 |

#### 大切なお客様へ

マイクロチップ社では、お客様にマイクロチップ社製品を効果的にお使いいただくために、分かりやすい文書を提供するように 努めています。このため、弊社はお客様のニーズに更に的確に応えられるように、出版物の改善を続けていきます。弊社の出版 物は、新しい巻や更新情報の発表に合わせて内容の見直しと充実が図られます。

本書に関してご意見やご質問をお持ちのお客様は、電子メールまたはファクスで弊社のマーケティングコミュニケーション部門にご連絡ください。電子メールアドレスは docerrors@mail.microchip.com、ファクス番号は 1-480-792-4150 (国際電話)です。ファクスの場合には、本書の巻末に用意されている「読者アンケート」のページをご利用ください。お客様からのご感想をお待ちしております。

#### 最新のデータシート

このデータシートの最新版を入手するには、以下のウェブ サイトから登録手続きを行ってください。

http://www.microchip.com

各ページのフッタに記載されている文書番号をご覧になると、データシートのバージョンを確認できます。文書番号の最後の文字がバージョン番号です (例: DS30000A は文書 DS30000 のバージョン A)。

#### 正誤表情報

現行のデバイスには、データシートとの動作上の微妙な相違点や推奨できる暫定的な対策を記した正誤表が存在することがあります。弊社では、デバイスや文書に関する問題を認識した時点で正誤表を発行します。正誤表には、該当するシリコンのバージョンと文書のバージョンが明記されます。

特定のデバイスに関して正誤表の有無を確認するには、以下のいずれかをご利用ください。

- マイクロチップ社のウェブ サイト: http://www.microchip.com

- 各国のマイクロチップ社営業所(最終ページ参照)

- Microchip Corporate Literature Center (米国 FAX: (480) 792-7277)

営業所または米国の Microchip Corporate Literature Center にお問い合わせになる場合、ご使用のデバイス、シリコンのバージョン、データシートのバージョン(文書番号を含む)をお伝えください。

#### お客様通知システム

マイクロチップ社のウェブ サイト (www.microchip.com/cn) で登録手続きを行うと、マイクロチップ社のすべての製品に関する最新情報を受信できるようになります。

**Preliminary**

ノート:

### 1.0 デバイス概要

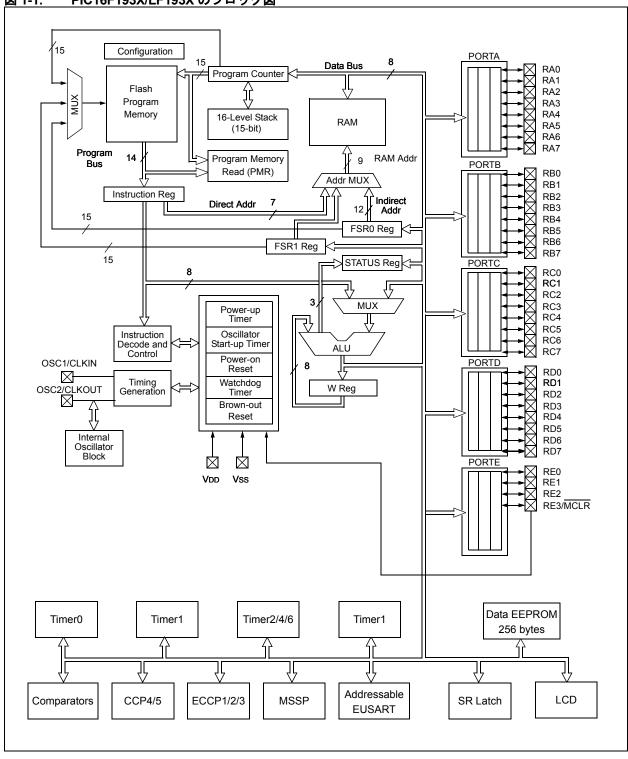

このデータ シートは、PIC16F193X/LF193X デバイス について説明しており、28 ピン /40 ピン /44 ピン パッケージで使用できます。図 1-1 に、PIC16F193X/LF193X デバイスのブロック図を示します。表 1-1 ではピンについて説明します。

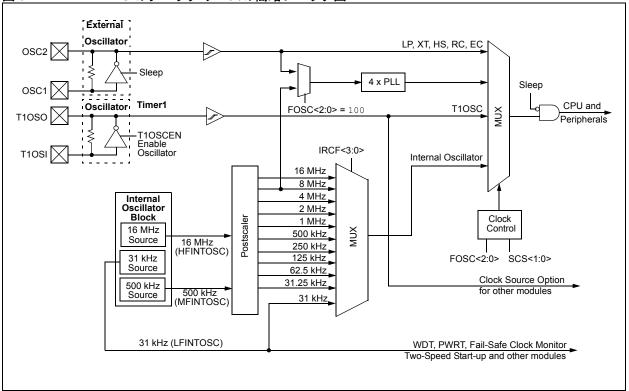

#### 図 1-1: PIC16F193X/LF193X のブロック図

#### 1.1 拡張型ミッドレンジ CPU

PIC16F193X/LF193X デバイスには、拡張型ミッドレンジの8ビット CPU コアが含まれています。CPU には49個の命令があり、割り込み発生時には自動で内容が保存される機能が搭載されています。ハードウェアスタックは16段あり、オーバーフローリセット機能とアンダーフローリセット機能があります。アドレス指定モードは、直接アドレス、間接アドレス、および相対アドレスがあります。2つのFSR(ファイルセレクトレジスタ)を使用してプログラムメモリやデータメモリの読み出しが可能です。

割り込み動作中、自動的に指定レジスタ内容がシャドウレジスタに保存され、通常動作に戻る際にレジスタ内容を回復できます。これにより、スタックの空間およびユーザーコードが節約されます。詳細は、4.5項「内容保存機能」を参照してください。

#### 1.1.1 オーバーフロー / アンダーフロー リセット機能付き 16 段スタック

PIC16F193X/LF193X デバイスには外部スタック メモリがあります (15 ビット幅 x 16 ワード)。通常動作時、スタックの深さは 16 ワードです。この機能が有効の場合、スタック オーバーフローまたはアンダーフローが生じると PCON レジスタの対応ビット (STKOVF または STKUNF) がセットされ、ソフトウェアがリセットされます。詳細は、2.4 項「スタック」を参照してください。

#### 1.1.2 FSR (ファイル セレクト レジスタ)

16 ビットの FSR が 2 つあります。これらの FSR は すべてのレジスタおよびプログラム メモリにアク セスでき、全メモリに対して 1 つのデータ ポイン タを許可できます。 FSR を使用してプログラム メ モリヘアクセスする場合、INDF レジスタヘアクセ スしてデータ フェッチする命令処理を行うため、追 加で 1 命令サイクルが必要です。また、FSR をサ ポートする新しい命令もあります。詳細は、2.5 項 「間接アドレス指定: INDF レジスタと FSR レジス タ」を参照してください。

#### 1.1.3 命令セット

CPU 機能をサポートするため、拡張型ミッドレンジ CPU には 48 個の命令があります。詳細は、**26.0 項** 「命令セットのまとめ」を参照してください。

表 1-1: PIC16F193X/LF193X のピン配置の説明

| Name                                              | Function            | Input<br>Type | Output<br>Type | Description                                               |

|---------------------------------------------------|---------------------|---------------|----------------|-----------------------------------------------------------|

| RA0/AN0/C12IN0-/C2OUT <sup>(1)</sup> /            | RA0                 | TTL           | CMOS           | General purpose I/O.                                      |

| $SRNQ^{(1)}/\overline{SS}^{(1)}/VCAP^{(2)}/SEG12$ | AN0                 | AN            | _              | A/D Channel 0 input.                                      |

|                                                   | C12IN0-             | AN            | _              | Comparator C1 or C2 negative input.                       |

|                                                   | C2OUT               | _             | CMOS           | Comparator C2 output.                                     |

|                                                   | SRNQ                | _             | CMOS           | SR Latch inverting output.                                |

|                                                   | SS                  | ST            | _              | Slave Select input.                                       |

|                                                   | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F193X only). |

|                                                   | SEG12               | _             | AN             | LCD Analog output.                                        |

| RA1/AN1/C12IN1-/SEG7                              | RA1                 | TTL           | CMOS           | General purpose I/O.                                      |

|                                                   | AN1                 | AN            | _              | A/D Channel 1 input.                                      |

|                                                   | C12IN1-             | AN            | _              | Comparator C1 or C2 negative input.                       |

|                                                   | SEG7                | _             | AN             | LCD Analog output.                                        |

| RA2/AN2/C2IN+/VREF-/CVREF/                        | RA2                 | TTL           | CMOS           | General purpose I/O.                                      |

| COM2                                              | AN2                 | AN            | _              | A/D Channel 2 input.                                      |

|                                                   | C2IN+               | AN            | _              | Comparator C2 positive input.                             |

|                                                   | VREF-               | AN            | _              | A/D Negative Voltage Reference input.                     |

|                                                   | CVREF               |               | AN             | Comparator Voltage Reference output.                      |

|                                                   | COM2                | _             | AN             | LCD Analog output.                                        |

| RA3/AN3/C1IN+/VREF+/                              | RA3                 | TTL           | CMOS           | General purpose I/O.                                      |

| COM3 <sup>(3)</sup> /SEG15                        | AN3                 | AN            | _              | A/D Channel 3 input.                                      |

|                                                   | C1IN+               | AN            |                | Comparator C1 positive input.                             |

|                                                   | V <sub>REF</sub> +  | AN            | _              | A/D Voltage Reference input.                              |

|                                                   | COM3 <sup>(3)</sup> |               | AN             | LCD Analog output.                                        |

|                                                   | SEG15               |               | AN             | LCD Analog output.                                        |

| RA4/C1OUT/CPS6/T0CKI/SRQ/                         | RA4                 | TTL           | CMOS           | General purpose I/O.                                      |

| CCP5/SEG4                                         | C1OUT               | _             | CMOS           | Comparator C1 output.                                     |

|                                                   | CPS6                | AN            | _              | Capacitive sensing input 6.                               |

|                                                   | T0CKI               | ST            | _              | Timer0 clock input.                                       |

|                                                   | SRQ                 | _             | CMOS           | SR Latch non-inverting output.                            |

|                                                   | CCP5                | ST            | CMOS           | Capture/Compare/PWM5.                                     |

|                                                   | SEG4                | _             | AN             | LCD Analog output.                                        |

| RA5/AN4/C2OUT <sup>(1)</sup> /CPS7/               | RA5                 | TTL           | CMOS           | General purpose I/O.                                      |

| $SRNQ^{(1)}/\overline{SS}^{(1)}/VCAP^{(2)}/SEG5$  | AN4                 | AN            |                | A/D Channel 4 input.                                      |

|                                                   | C2OUT               | _             | CMOS           | Comparator C2 output.                                     |

|                                                   | CPS7                | AN            |                | Capacitive sensing input 7.                               |

|                                                   | SRNQ                | _             | CMOS           | SR Latch inverting output.                                |

|                                                   | SS                  | ST            | _              | Slave Select input.                                       |

|                                                   | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F193X only). |

|                                                   | SEG5                | _             | AN             | LCD Analog output.                                        |

OD =オープン ドレイン  $I^2C^{TM} = I^2C$  レベルのシュミット

トリガ入力

HV = 高電圧 (High Voltage) XTAL = クリスタル 注 1: APFCON レジスタを介してピン機能を選択できます。

**2:** PIC16F193X デバイスのみ。

**3:** PIC16F1933/1936/1938/PIC16LF1933/1936/1938 デバイスのみ。

**4:** PORTD は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

5: RE<2:0> は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

表 1-1: PIC16F193X/LF193X のピン配置の説明 (続き)

| Name                                                                    | Function | Input<br>Type | Output<br>Type | Description                                                                                     |

|-------------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------|

| RA6/OSC2/CLKOUT/VCAP <sup>(2)</sup> /                                   | RA6      | TTL           | CMOS           | General purpose I/O.                                                                            |

| SEG1                                                                    | OSC2     | _             | XTAL           | Crystal/Resonator (LP, XT, HS modes).                                                           |

|                                                                         | CLKOUT   | _             | CMOS           | Fosc/4 output.                                                                                  |

|                                                                         | VCAP     | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F193X only).                                       |

|                                                                         | SEG1     | _             | AN             | LCD Analog output.                                                                              |

| RA7/OSC1/CLKIN/SEG2                                                     | RA7      | TTL           | CMOS           | General purpose I/O.                                                                            |

|                                                                         | OSC1     | XTAL          | _              | Crystal/Resonator (LP, XT, HS modes).                                                           |

|                                                                         | CLKIN    | CMOS          | _              | External clock input (EC mode).                                                                 |

|                                                                         | SEG2     | _             | AN             | LCD Analog output.                                                                              |

| RB0/AN12/CPS0/CCP4/SRI/INT/<br>SEG0                                     | RB0      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                         | AN12     | AN            | _              | A/D Channel 12 input.                                                                           |

|                                                                         | CPS0     | AN            | _              | Capacitive sensing input 0.                                                                     |

|                                                                         | CCP4     | ST            | CMOS           | Capture/Compare/PWM4.                                                                           |

|                                                                         | SRI      | _             | ST             | SR Latch input.                                                                                 |

|                                                                         | INT      | ST            | _              | External interrupt.                                                                             |

|                                                                         | SEG0     | _             | AN             | LCD analog output.                                                                              |

| RB1/AN10/C12IN3-/CPS1/P1C/<br>VLCD1                                     | RB1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                         | AN10     | AN            | _              | A/D Channel 10 input.                                                                           |

|                                                                         | C12IN3-  | AN            | _              | Comparator C1 or C2 negative input.                                                             |

|                                                                         | CPS1     | AN            | _              | Capacitive sensing input 1.                                                                     |

|                                                                         | P1C      | _             | CMOS           | PWM output.                                                                                     |

|                                                                         | VLCD1    | AN            | _              | LCD analog input.                                                                               |

| RB2/AN8/CPS2/P1B/VLCD2                                                  | RB2      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                         | AN8      | AN            | _              | A/D Channel 8 input.                                                                            |

|                                                                         | CPS2     | AN            | _              | Capacitive sensing input 2.                                                                     |

|                                                                         | P1B      | _             | CMOS           | PWM output.                                                                                     |

|                                                                         | VLCD2    | AN            | _              | LCD analog input.                                                                               |

| RB3/AN9/C12IN2-/CPS3/<br>CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup> /VLCD3 | RB3      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                         | AN9      | AN            | _              | A/D Channel 9 input.                                                                            |

|                                                                         | C12IN2-  | AN            | _              | Comparator C1 or C2 negative input.                                                             |

|                                                                         | CPS3     | AN            | _              | Capacitive sensing input 3.                                                                     |

|                                                                         | CCP2     | ST            | CMOS           | Capture/Compare/PWM2.                                                                           |

|                                                                         | P2A      |               | CMOS           | PWM output.                                                                                     |

|                                                                         | VLCD3    | AN            | _              | LCD analog input.                                                                               |

記号の説明:AN = アナログ入出力

CMOS = CMOS 互換入出力

TTL= TTL 互換入力 ST = CMOS レベルのシュミットトリガ入力 HV = 高電圧 (High Voltage) XTAL = クリスタル OD = オープン ドレイン  $I^2C^{TM} = I^2C$  レベルのシュミットトリガ入力

注 1: APFCON レジスタを介してピン機能を選択できます。

2: PIC16F193X デバイスのみ。

**3:** PIC16F1933/1936/1938/PIC16LF1933/1936/1938 デバイスのみ。

**4:** PORTD は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

5: RE<2:0> は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

#### 表 1-1: PIC16F193X/LF193X のピン配置の説明 (続き)

| Name                                                                                    | Function | Input<br>Type    | Output<br>Type | Description                                                                                     |

|-----------------------------------------------------------------------------------------|----------|------------------|----------------|-------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4/P1D/COM0                                                                  | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                                         | AN11     | AN               | _              | A/D Channel 11 input.                                                                           |

|                                                                                         | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                     |

|                                                                                         | P1D      | _                | CMOS           | PWM output.                                                                                     |

|                                                                                         | COM0     | _                | AN             | LCD Analog output.                                                                              |

| RB5/AN13/CPS5/P2B/CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> /T1G <sup>(1)</sup> /COM1 | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                                         | AN13     | AN               | _              | A/D Channel 13 input.                                                                           |

|                                                                                         | CPS5     | AN               | _              | Capacitive sensing input 5.                                                                     |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                     |

|                                                                                         | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.                                                                           |

|                                                                                         | P3A      | _                | CMOS           | PWM output.                                                                                     |

|                                                                                         | T1G      | ST               | _              | Timer1 Gate input.                                                                              |

|                                                                                         | COM1     | _                | AN             | LCD Analog output.                                                                              |

| RB6/ICSPCLK/ICDCLK/SEG14                                                                | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                                         | ICSPCLK  | ST               | _              | Serial Programming Clock.                                                                       |

|                                                                                         | ICDCLK   | ST               | _              | In-Circuit Debug Clock.                                                                         |

|                                                                                         | SEG14    | _                | AN             | LCD Analog output.                                                                              |

| RB7/ICSPDAT/ICDDAT/SEG13                                                                | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up. |

|                                                                                         | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                 |

|                                                                                         | ICDDAT   | ST               | CMOS           | In-Circuit Data I/O.                                                                            |

|                                                                                         | SEG13    | _                | AN             | LCD Analog output.                                                                              |

| RC0/T1OSO/T1CKI/P2B <sup>(1)</sup>                                                      | RC0      | ST               | CMOS           | General purpose I/O.                                                                            |

|                                                                                         | T1OSO    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                   |

|                                                                                         | T1CKI    | ST               | _              | Timer1 clock input.                                                                             |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                     |

| RC1/T1OSI/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup>                                       | RC1      | ST               | CMOS           | General purpose I/O.                                                                            |

|                                                                                         | T1OSI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                   |

|                                                                                         | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                           |

|                                                                                         | P2A      | _                | CMOS           | PWM output.                                                                                     |

| RC2/CCP1/P1A/SEG3                                                                       | RC2      | ST               | CMOS           | General purpose I/O.                                                                            |

|                                                                                         | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                           |

|                                                                                         | P1A      | -                | CMOS           | PWM output.                                                                                     |

|                                                                                         | SEG3     | _                | AN             | LCD Analog output.                                                                              |

| RC3/SCK/SCL/SEG6                                                                        | RC3      | ST               | CMOS           | General purpose I/O.                                                                            |

|                                                                                         | SCK      | ST               | CMOS           | SPI clock.                                                                                      |

|                                                                                         | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> CTM clock.                                                                       |

|                                                                                         | SEG6     |                  | AN             | LCD Analog output.                                                                              |

記号の説明:AN = アナログ入出力

CMOS = CMOS 互換入出力

OD = オープン ドレイン  $I^2C^{TM} = I^2C$  レベルのシュミットトリガ入力

TTL= TTL 互換入力

ST = CMOS レベルのシュミットトリガ入力

HV = 高電圧 (High Voltage) XTAL = クリスタル

注 1: APFCON レジスタを介してピン機能を選択できます。2: PIC16F193X デバイスのみ。

- **3:** PIC16F1933/1936/1938/PIC16LF1933/1936/1938 デバイスのみ。

- **4:** PORTD は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

- 5: RE<2:0> は、PIC16F1934/1937/1939/PIC16LF1934/1937/1939 デバイスでのみ有効。

PIC16F193X/LF193X のピン配置の説明 (続き) 表 1-1:

| RC4/SDISDATIG <sup>II</sup> /SEGII         RC4/SDISDATIG <sup>II</sup> /SEGII         RC4/SDISDATIG <sup>II</sup> /SEGII         ST         CMOS         General purpose I/O.           SDA         FC         OP         PCP data input           SDA         PC         OP         PCP data input           RC5         SBGII         —         AN         LCD Analog output.           RC5/SDO/SEGI0         BCS         ST         CMOS         SPI data output.           RC6/TX/CK/CCP3/P3A/SEG9         RC6         ST         CMOS         General purpose I/O.           TX         —         CMOS         General purpose I/O.           TX         —         CMOS         USART synchronous transmit.           CCC93         ST         CMOS         USART synchronous transmit.           RC7/RX/DT/P3B/SEG8         RC         ST         CMOS         General purpose I/O.           RC7/RX/DT/P3B/SEG8         RX         T         USART synchronous input.           RC7/RX/DT/P3B/SEG8         RD         ST         CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Name                                  | Function | Input<br>Type    | Output<br>Type | Description                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|------------------|----------------|---------------------------------------------------|

| SDA   PC   OD   PC   Mata input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RC4/SDI/SDA/T1G <sup>(1)</sup> /SEG11 | RC4      | ST               | CMOS           | General purpose I/O.                              |

| TIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       | SDI      | ST               | _              | SPI data input.                                   |

| SEG11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | SDA      | I <sup>2</sup> C | OD             | I <sup>2</sup> C <sup>TM</sup> data input/output. |

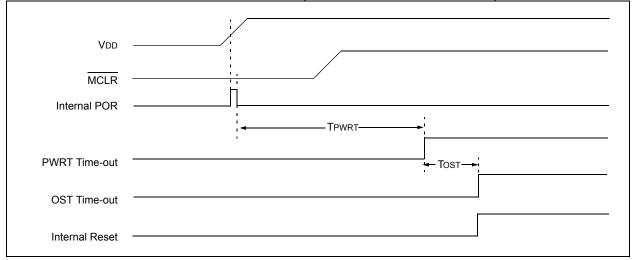

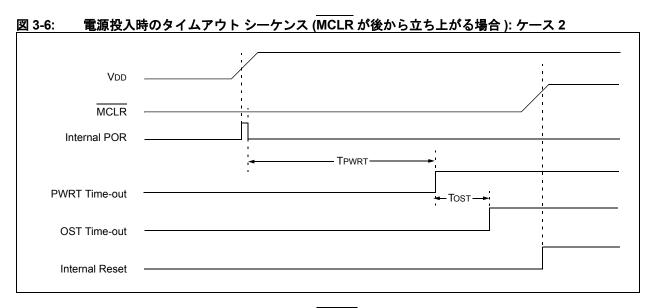

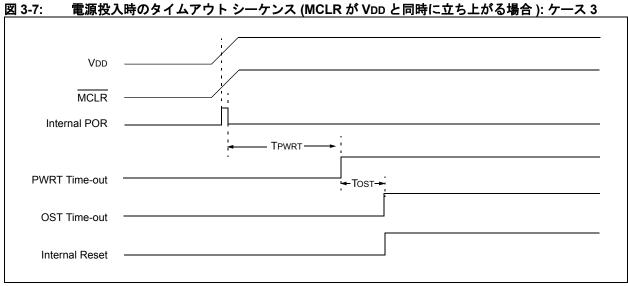

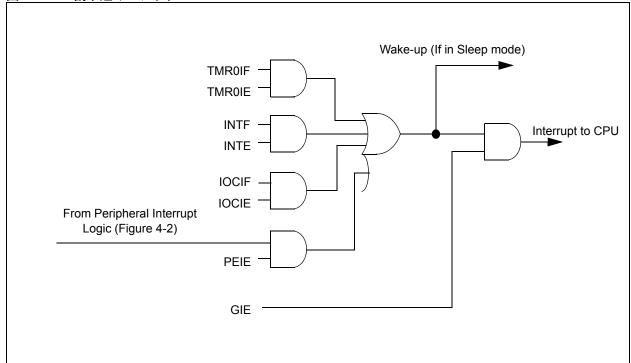

| RC5/SDO/SEG10         RC5         ST         CMOS         General purpose I/O.           RC6         SG10         −         CMOS         SPI data output.           RC6/TX/CK/CCP3/P3A/SEG9         RC6         ST         CMOS         General purpose I/O.           RC6/TX/CK/CCP3/P3A/SEG9         RC6         ST         CMOS         USART synchronous clock.           CCP3         ST         CMOS         Capture/Compare/PWM3.           CCP3         ST         CMOS         Capture/Compare/PWM3.           RC7         ST         CMOS         Capture/Compare/PWM3.           RC7         ST         CMOS         Capture/Compare/PWM3.           RC7         ST         CMOS         Capture/Compare/PWM3.           RC7         ST         CMOS         General purpose I/O.           RC7         ST         CMOS         General purpose I/O.           RC7         ST         CMOS         General purpose I/O.           RD0         ST         CMOS         General purpose I/O.           CCM3         -         AN         LCD Analog output.           RD14/CPS8/CPS1/PS9/CP4         RD1         ST         CMOS         General purpose I/O.           CCP3         AN         - </td <td></td> <td>T1G</td> <td>ST</td> <td>_</td> <td>Timer1 Gate input.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       | T1G      | ST               | _              | Timer1 Gate input.                                |